-

光控计数器设计,光控计数器电路图

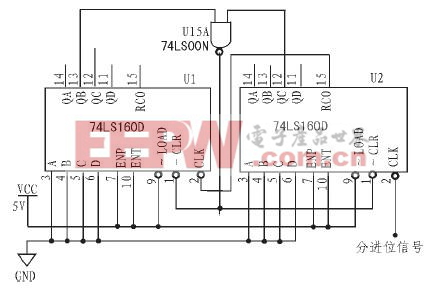

计数器如何设计?利用减计数Rd=0,反向=0,CPd=1,实现计数器按8421码递减进行减计数。利用借位输出端反向BO与下一级的CPd连接,实现计数器之间的级联。利用预置数反向L...

发布时间:2024-03-03 分类:资讯 浏览:34 评论:0

-

verilog计数器设计,verilog计数器设计带进位

用verilog程序设计一个具有异步清零功能的24进制计数器编译,通过后,添加波形文件,如下图所示。保存,点击波形仿真按钮,开始波形仿真,如下图所示。仿真成功,结果如下图所示。波...

发布时间:2024-03-02 分类:资讯 浏览:32 评论:0

-

触发器设计同步计数器,同步触发器和计数器的设计应用

如何用触发器设计计数器?1、设计方案:用触发器组成计数器。触发器具有0和1两种状态,因此用一个触发器就可以表示一位二进制数。如果把n个触发器串起来,就可以表示n位二进制数。2、...

发布时间:2024-02-29 分类:资讯 浏览:34 评论:0

-

关于quartus计数器设计的信息

基于Quartus2设计模100计数器,用两个数码管显示将两位数拆开,十位和个位;用除法和取余函数就可以得到十位和个位;如c=36a=c/10;b=c%10则,a=3;b=6再...

发布时间:2024-02-19 分类:资讯 浏览:31 评论:0

-

bcd计数器设计,bcd计数器输出函数

数字电路制作一个加减计数器如果将T′触发器之间按二进制减法规则连接,就可以得到二进制减法计数器。根据二进制减法计数规则。若低位触发器已经为0,则再输入一个减法计数脉冲后应翻转为1...

发布时间:2024-02-13 分类:资讯 浏览:43 评论:0

-

计数器电路设计,计数器电路设计实验

用两块74ls193芯片和必要的门电路设计一个模19的加法计数器,电路图和设...使用常开触发器将最终的控制计数器清零的信号转换为清零信号Rst。一)首先要使用74LS192或4...

发布时间:2024-02-11 分类:资讯 浏览:44 评论:0

-

串行累加器的设计,串行计数器

单片机问题单片机复位时,程序计数器PC的值为0000H,所以编程时在ROM的起始位置0000H上写上一条跳转到主程序的无条件跳转指令,不能写上MAP:DB2BH,3FH也不能写...

发布时间:2024-02-08 分类:资讯 浏览:38 评论:0

-

计数器设计应用,计数器设计应用有哪些

74LS163计数器及其应用1、ls163是一个很简单的计数芯片,当CEP、CET接高时,芯片可以正常计数,DO~D3是置位数据的输入端,Q1~Q4是数据的输出端,而置数端和清零...

发布时间:2024-02-07 分类:资讯 浏览:43 评论:0

-

设计输入的计数器,设计计数器时应选用什么触发器

如何设计N进制计数器?1、首先需要构建一个3进制计数器。CT74LS161本身是4位二进制计数器,因此需要进行一些改动。将CLR和LD连接到低电平,CLK连接到时钟信号源。将Q3...

发布时间:2024-02-02 分类:资讯 浏览:47 评论:0

-

设计100进制计数器,100进制计数器实验报告

基于Quartus2设计模100计数器,用两个数码管显示数码管段选表。延时函数。uchari;变量i;wk=1;打开位选,P0=0xf7;11110111第4位数码...

发布时间:2024-02-01 分类:资讯 浏览:38 评论:0

- 最近发表

- 标签列表

- 友情链接