4位全加器的设计,四位全加器电路设计

作者:admin 发布时间:2024-01-31 15:00 分类:资讯 浏览:40 评论:0

什么是全加器?

1、英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。

2、全加器英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。

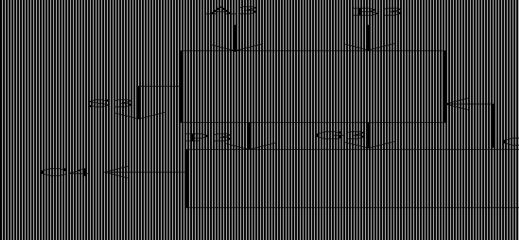

3、全加器逻辑图:二进制全加器 用于门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。

使用一个4位二进制全加器,设计将8421码转换成余三码的电路,画出设计的...

用4位二进制并行加法器实现8421码到余3码的转换,只需从4位二进制并行加法器的输入端AAA2和A1输入8421码,而从输入端BBB2和B1输入二进制数0011,进位输入端C0接上“0”。

就当是2个4位输入,1个4位输出的全加器,因为BCD码是4位的。 一个全加器进行a+b计算。 另一个全加器对第一个全家器的结果进行修正。 BCD码因为从0-9,只有10个有效数字。

由8421码加3后形成的余3码是一种BCD码,是由8421码加3后形成的(即余3码是在8421码基础上每位十进制数BCD码再加上二进制数0011得到的)。

假设要实现A X B,利用门电路搭一个2-4译码器。2-4译码器的输入信号为A;然后用2-4译码器的输出控制一个4路选择器,4路选择器的4个输入分别是0,B,B+B,B+B+B,这部分用二位全加器实现。

利用可编程逻辑器件设计实现4位二进制并行加法器。

算术运算单元ALU的设计要求:进行两个四位二进制数的运算。

EDA技术就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言HDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

VHDL(VHSIC Hardware Description Language)是随着可编程逻辑器件的开展而开展起来的一种硬件描述语言。

现场可编程门阵列(FPGA)是可编程器件。

FPGA原理(Field-Programmable Gate Array):FPGA是一种可编程逻辑器件,可以通过编程来实现数字电路的功能。它由一系列可编程的逻辑单元(Look-Up Tables,LUTs)和触发器(Flip-Flops)组成,以及可配置的连线和I/O接口。

相关推荐

欢迎 你 发表评论:

- 资讯排行

- 标签列表

- 友情链接