VerilogHDL程序设计教程,veriloghdl入门

作者:admin 发布时间:2024-03-06 13:45 分类:资讯 浏览:36 评论:0

Verilog数字系统设计教程的作品目录

1、》作为蓝本,本书比较全面地、详细地介绍了Verilog的基本语法。如果是其他初学者,可以直接借助《Verilog数字系统设计教程(第二版)》和本书即能全面掌握Verilog的语法,这是学习FPGA的第一步,也是必不可少的一步。

2、个人认为。入门的话:王金明编著 《数字系统设计与Verilog HDL 》,讲得比较细,而且基础实验都有。

3、https://pan.baidu.com/s/1FeRMQSG0bGCcTahtthGy3Q 提取码:1234 本书以Verilog HDL语言为蓝本,结合Quartus II软件,通过丰富的实例,从实验、实践、实用的角度,详细介绍了FPGA在电子系统中的应用。

4、《Verilog HDL高级数字设计(第2版)(英文版)》既可作为电子与通信、电子科学与技术、自动控制、计算机等专业领域的高年级本科生和研究生的教材或参考资料,也可用于电子系统设计及数字集成电路设计工程师的专业技术培训。

5、《Verilog HDL高级数字设计(第2版)(英文版)》是2010年电子工业出版社出版的图书,作者是西勒提(Michael D.Ciletti)。

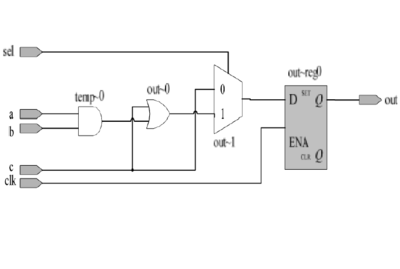

怎样用Verilog实现4选1数据选择器

数据选择器 释义:数据选择器(data selector) 根据给定的输入地址代码,从一组输入信号中选出指定的一个送至输出端的组合逻辑电路。有时也把它叫做多路选择器或多路调制器(multiplexer)。

用4选1数据选择器实现该函数,A,B分别接入数据选择器的A1,A0地址输入端,C作为数据输入端,上式化为4选1数据选择器的标准逻辑式:Y=A1A0(C+C)+A1A0C=A1A0·0+A1A0·0+A1A0·1+A1A0·C。

选1数据选择器的元件符号如下图所示,其中D0、DDD3是4位数据输入端,A0和A0是控制输入端,Y是数据输出端。当A1A0=00时,输出Y=D1;A1A0=01时,Y=D1;A1A0=10时,Y=D2;A1A0=11,Y=D3。

直接看输入的bit2和bit3,如果不是00输出为0,否则输出为1。

步骤如下:将两个四选一数据选择器的VCC和GND引脚连接至电源正负电极,进行电源连接。将第一个四选一数据选择器的输出端S0输入连接到第二个四选一数据选择器的控制端S1输入,以实现控制输入信号的选择。

本人刚开始接触Verilog,如何用比较简单的Verilog代码实现电子时钟设计...

hX; end // X means 1s led code ...default: begin led1=0;led2=0; end endcase endmodule 打完整也可以,不过共阴共阳的LED代码不一样。根据自己的LED,把LED显示数字的代码加在相应位置就行了。

A,B是23或60的计数变量,C,D是你的输出端。记得在实体进行声明。

其实就是编写一个分频程序吧,把你原有的时钟50MHz分频成100Hz。大概就是你要把50000000个方波分频成100个方波。

提供一个时钟计数、设置、闹钟的verilog代码,供参考。

Verilog设计流程问题

1、从设计方法可以分成自顶而下(top-down)和自底而上两种方法。

2、如果某个设计的处理流程分为若干步骤,而且整个数据处理是 “ 单流向 ” 的,即没有反馈或者迭代运算,前一个步骤的输出是下一个步骤的输入,则可以考虑采用流水线设计方法来提高系统的工作频率。

3、每个Verilog程序包括四个主要部分:端口定义、I/O说明、内部信号声明、功能定义。Verilog HDL是一种用于数字逻辑电路设计的语言。用Verilog HDL描述的电路设计就是该电路的Verilog HDL模型。

4、下面是一个简单的 Verilog HDL 代码,可以实现六位数码管动态显示从左到右为123456的效果。

5、因为在默认情况下,verilog语言在进行运算时,会根据参与运算(包括结果)的变量的最大长度来进行,从而确保运算的正确性。

6、布局,布线也是由软件自动规划在FPGA芯片里面的连接问题。(注意是芯片里面的连接)规划好了,下载进芯片的话,芯片里面就是那种规划的结构了 (理解成没有下载程序的芯片是一张白纸)。

相关推荐

欢迎 你 发表评论:

- 资讯排行

- 标签列表

- 友情链接